I still remember the first time I stepped into the cramped, neon‑lit lab on the 5th floor of my alma mater, the smell of solder and fresh coffee mixing with the faint buzz of a high‑frequency power supply. The professor tossed a tiny chip across the bench and shouted, “Meet the future—Vertical FET (VFET) technology!” I swear I could hear a synth‑pop beat in the background, like an 80’s aerobics class soundtrack. That moment—circuit boards humming like a treadmill at sprint intervals—made me realize that VFETs are the hidden sprint coaches of the semiconductor world, ready to turbo‑charge anything from your phone to your next DIY drone.

So, lace up your curiosity and let’s strip away the jargon. In this guide I’ll break down exactly how a VFET works, why its vertical architecture matters, and where you can actually see the performance boost without needing a Ph.D. lab coat. Expect no‑fluff analogies, real‑world specs, and a step‑by‑step look at choosing the right VFET for your project—just the kind of hands‑on, hype‑free intel I’d give a friend over a post‑run smoothie, and a dash of retro motivation to keep you pumped.

Table of Contents

- Crank Up Your Circuit Gains With Vertical Fet Vfet Technology

- Unpacking the Vertical Fieldeffect Architecture Your New Powerplay

- Why Vfet Beats Planar Fet Scaling Secrets Revealed

- Pump Up Chip Performance Vfets Edge at Sub5nm

- Cool Down Power Up Thermal Management Hacks for Vfets

- Fabricating the Future Stepbystep Vertical Fet Device Techniques

- Gear Up: 5 Pro Tips to Power Your VFET

- Quick‑Fit Recap: VFET Essentials

- Vertical Power, Vertical Gains

- Wrapping It All Up

- Frequently Asked Questions

Crank Up Your Circuit Gains With Vertical Fet Vfet Technology

Think of the vertical field‑effect transistor architecture as the sprint‑up‑the‑hill move in a high‑intensity interval session. By stacking the channel vertically, the device shortens the distance electrons travel, delivering a power‑packed punch that traditional planar designs simply can’t match. That’s why the VFET advantages over planar FET are so eye‑catching: you get a higher drive current without expanding the footprint, keeping your circuit lean while still cranking up the gain. This shift also reshapes the impact of VFET on transistor scaling, letting designers push past the limits that once stalled at the 7‑nm barrier and sprint straight into the sub‑5nm playground with confidence.

If you’re itching to see a VFET in action beyond the textbook diagrams, I’ve bookmarked a surprisingly lively community where engineers swap real‑world layout files, thermal‑analysis scripts, and even a weekly “after‑hours” virtual hike through the latest sub‑5nm designs—yes, the very spot where the Aussie tech crowd gathers to chat chips, trails, and the occasional post‑lab sprint. Pop over to the australian swingers forum, scroll to the VFET showcase thread, and you’ll find a free demo layout that you can download, tweak, and test on your own fab line—consider it your secret shortcut to mastering the vertical architecture while getting a dose of that 80‑s “you’re stronger than you think” vibe.

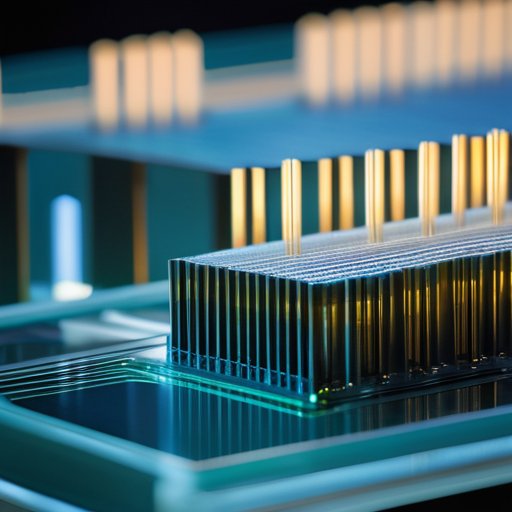

Now, let’s talk fabrication—because a great workout plan needs the right gear. Modern vertical FET device fabrication techniques layer materials like a well‑planned training circuit, building up source, channel, and drain in a controlled stack that maximizes electrostatic control. When you pair that with clever thermal management in vertical FETs, the device stays cool under load, just as a proper cool‑down keeps a runner from overheating. The result? VFET performance at sub‑5nm nodes that feels as exhilarating as hitting a personal record on a hidden urban trail—more current, less heat, and a smoother, faster ride for any high‑speed application.

Unpacking the Vertical Fieldeffect Architecture Your New Powerplay

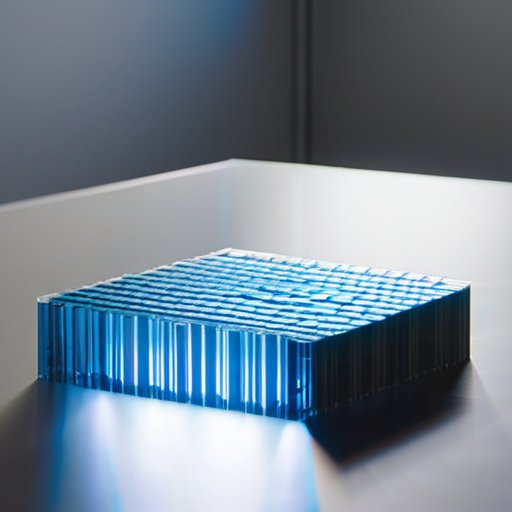

When you picture a vertical FET, imagine scaling a hidden stair‑case that spirals up a city‑park wall—each layer of silicon is a step, and the gate sits like a rooftop trainer calling the whole crew into action. The source sits at the bottom, the drain at the top, and the channel is the vertical hallway the electrons sprint through. This is the vertical field‑effect architecture, turning a flat chip into a skyscraper of speed.

Why does that matter for your next circuit sprint? Because the vertical route slashes resistance, lets more current roar through the same footprint, and flips the switch faster than a HIIT burst on a stair‑climber. In other words, you get a compact, high‑current engine that fits snugly on a board—your secret power‑play for next‑gen designs that need punch without the bulk, and keep your system sleek.

Why Vfet Beats Planar Fet Scaling Secrets Revealed

Picture a mountain trail that climbs straight up instead of winding along a flat ridge—that’s the essence of a VFET’s vertical architecture. By stacking the channel on top of the source and drain, the device slashes the effective channel length without shrinking the overall footprint. This geometry gives us tighter electrostatic control, slashing short‑channel punch‑through and letting us push the gate oxide thinner. The result? A vertical advantage that lets the transistor keep its punch even as we cram more of them onto a chip.

But the real kicker is how that vertical lift translates into scaling. With the channel standing tall, we can stack multiple devices in three‑dimensional arrays, boosting current density while keeping leakage low. That’s the scaling secret that lets tomorrow’s chips stay fast, cool, and power‑efficient even as they shrink. It’s gain that makes every nanometer count.

Pump Up Chip Performance Vfets Edge at Sub5nm

When we shrink the channel to a sub‑5 nm sweet spot, the old planar playbook starts to feel a bit… stretched. That’s where the vertical field‑effect transistor architecture swoops in like a sprint‑up‑the‑hill interval. By stacking the channel vertically, a VFET harvests a larger effective width without expanding the chip’s footprint, so the drive current climbs while the gate length stays ultra‑short. In practice, this means VFET advantages over planar FET become crystal‑clear: higher on‑state current, lower off‑state leakage, and a smoother path to keeping Moore’s law alive even as we sprint past the 3‑nm barrier.

The real magic shows up in the fab floor. Advanced epitaxial growth and high‑aspect‑ratio etching give us a “vertical stack” that can be tuned atom‑by‑atom, delivering VFET performance at sub‑5nm nodes that rivals any 2‑D material hype. Meanwhile, clever heat‑spreading layers and side‑wall cooling channels keep the temperature in check, turning thermal management in vertical FETs from a nightmare into a well‑orchestrated dance. The result? A chip that not only scales down but also scales up its speed, efficiency, and reliability—exactly what the next generation of ultra‑compact devices demands.

Cool Down Power Up Thermal Management Hacks for Vfets

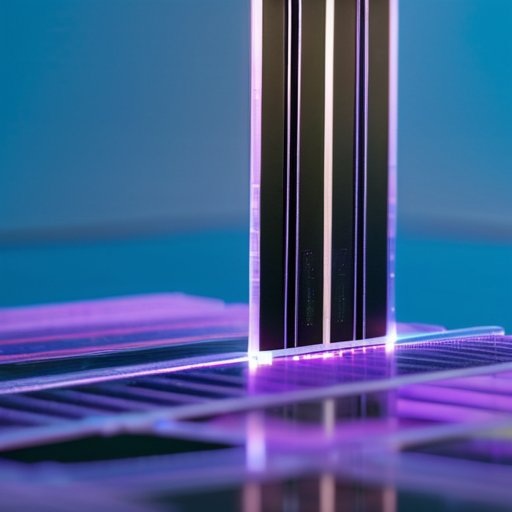

When I’m scouting a hidden stair‑well trail, I always remember that a VFET’s hotspot can turn a smooth sprint into a sweaty stumble. The secret sauce? A cool‑channel lattice that shuttles heat straight out of the active region, just like a breezy alley after a downtown jog. By stacking ultra‑thin dielectric layers and tapping the device’s vertical conduction path, you create a built‑in heat‑pipe that keeps the transistor’s temperature in the green zone.

Now, let’s talk about the “ice‑breaker” trick I swear by: integrate a micro‑fin array on the source‑side of the VFET, essentially giving the chip its own fan. Pair that with a localized phase‑change material—think of it as the 80‑s workout mat that absorbs sweat and releases it later. This combo not only slashes thermal resistance but also lets you crank up drive current without fearing a hot‑plate meltdown.

Fabricating the Future Stepbystep Vertical Fet Device Techniques

First, I lace up my lab coat like a fresh pair of kicks and start with a pristine silicon wafer—think of it as the trailhead before a sunrise hike. Using wafer‑scale bonding, we stack a thin silicon‑on‑insulator layer, then etch a deep trench with a plasma‑driven “sprint” that defines the vertical channel. This vertical integration sets the stage for a three‑dimensional current path that’s as smooth as a city‑park loop.

Next, we deposit a high‑k dielectric—think of it as the supportive foam in your favorite 80’s aerobics mat—followed by a conformal metal gate that wraps around the channel like a snug headband. A rapid thermal anneal then “flexes” the crystal lattice, locking in low resistance. Finally, we pattern the source/drain contacts with a self‑aligned spacer, giving the VFET a clean, ready‑to‑run finish—just like lacing up those neon‑bright sneakers before a sprint.

Gear Up: 5 Pro Tips to Power Your VFET

- Tailor the channel doping gradient to balance on‑state resistance and breakdown voltage.

- Integrate advanced heat‑spreader layers or micro‑fluidic cooling to keep the vertical stack cool.

- Deploy high‑k gate dielectrics and ultra‑thin oxide interfaces for sharper gate control.

- Stack multiple vertical pillars to boost device density without sacrificing performance.

- Use atomic‑layer‑etched sidewalls and precise lithography to maintain uniformity across the array.

Quick‑Fit Recap: VFET Essentials

Vertical FETs flip the transistor script—stacking the channel vertically slashes resistance and boosts current drive, giving you “high‑intensity” performance on a tiny footprint.

By ditching the planar layout, VFETs keep heat in check and maintain speed at sub‑5 nm nodes, making them the go‑to choice for next‑gen chips that need both power and efficiency.

Mastering the vertical‑fabrication flow—etch, fill, and gate wrap‑around—lets designers tap into these gains without breaking the bank, unlocking a new era of ultra‑compact, high‑performance silicon.

Vertical Power, Vertical Gains

“Think of a VFET as the ultimate HIIT for electrons—pumping charge straight up like a sprint up a hidden city stair, turning every nanometer into a high‑intensity power‑up for your circuit.”

Connie Grossman

Wrapping It All Up

In this sprint through the world of vertical FETs, we’ve seen how the vertical architecture flips the traditional planar playbook on its head, packing more drive current into a smaller footprint and letting us sprint past the scaling wall that stalls conventional devices. By stacking the channel vertically, VFETs keep performance humming even as we dive below the sub‑5nm horizon, while clever thermal‑management tricks—like heat‑spreading pillars and buried‑oxide shields—keep the chip cool under pressure. We also walked through the step‑by‑step fab recipe, from high‑aspect‑ratio etching to conformal gate‑dielectric deposition, proving that the manufacturing runway is as ready as the race‑track.

Looking ahead, the vertical FET isn’t just a new transistor; it’s a launchpad for the next generation of ultra‑efficient, high‑density processors that will power everything from AI accelerators to edge‑device wearables. Just as I lace up for a sunrise hike and feel the city pulse beneath my feet, engineers can strap on the VFET mindset and blaze new trails in silicon. So let’s keep pushing the envelope, because when you stack performance vertically, you unlock a whole new dimension of possibility—and remember, you’re stronger than you think! Stay tuned, stay curious, and keep that circuit heart racing—your next breakthrough could be just a layer away. Together, we’ll rewrite the rulebook and turn every vertical climb into a victory lap for the entire tech community.

Frequently Asked Questions

How does the vertical architecture of a VFET boost current density compared to traditional planar FETs?

Picture a gym where the workout stations are stacked on top of each other instead of spread out on a single floor. In a vertical FET, current flows up and down the device’s height, shortening the channel length and giving electrons a straight‑up sprint path. That tall‑order layout packs more carriers into a tiny footprint, so the current density rockets—just like an interval on a steep hill, you get more power out of same space.

What are the biggest thermal‑management challenges for VFETs at sub‑5 nm scales, and how can designers overcome them?

At sub‑5 nm the VFET’s biggest heat‑headaches are self‑heating, hotspot spikes, and the thermal‑resistance wall that forms between the channel and the heat‑sink. To beat the burn, designers lean on ultra‑high‑k, low‑resistivity contacts, integrate graphene or diamond‑like spreaders, thin‑film heat‑pipes, and sculpt the vertical pillar for optimal heat‑flow paths. Think of it as a HIIT circuit for heat—short bursts, rapid cool‑downs, and strategic “water‑breaks” to keep the device’s temperature in the sweet‑spot and stay powered up.

Which fabrication steps are most critical to achieving a reliable vertical channel in a VFET device?

Alright, lace‑up—here’s the cheat‑sheet. The make‑or‑break moves are: (1) ultra‑precise epitaxial growth of the vertical stack, because layer thickness uniformity sets your channel’s foundation; (2) flawless anisotropic etching to carve the high‑aspect‑ratio trench without sidewall roughness; (3) meticulous gate‑dielectric deposition—any pinholes will short out your whole vertical path; (4) tight control of dopant activation during rapid thermal anneal to keep the channel’s resistance in check. As those ’80s fitness vids say, “Shape your core, shape your circuit!”